### **RAKE** Correlator

Roy Ha Graham Hull Lakshmi Sreekumar Jason White

Why should you care?

Channel Model

What is it? How does it work?

Our RAKE finger Specs

## Why should you care?

- Wireless Devices

- DSP

- Vocoder

- RAKE Correlator

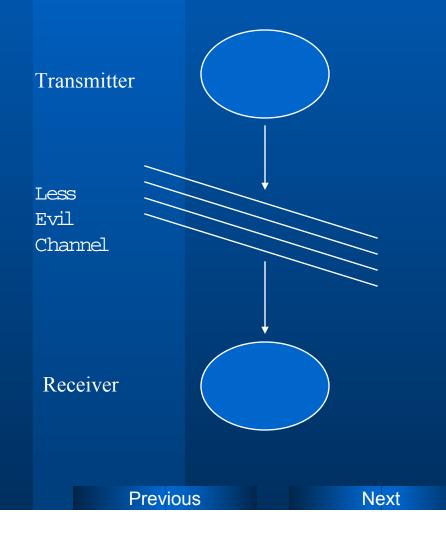

### **Channel** Model

- Standard, Basic

Channel Model

- Additive noise

- Amplitude Changes

- Phase Changes

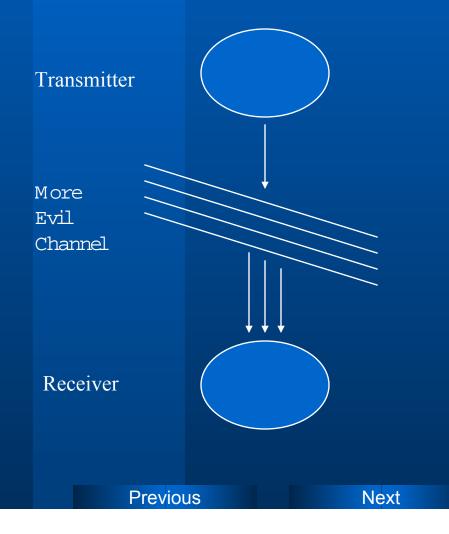

### **Channel** Model

More "realistic" channel model

- Additive noise

- Multiple Paths

- Amplitude Changes

- Phase Changes

- Added Together at receiver

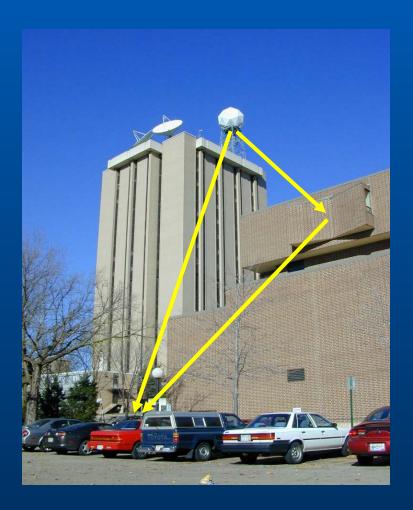

### **Channel** Model

#### Reasons

- Signals bounce off buildings

- Amplitude, phase distortion

- Delayed paths summed with direct path

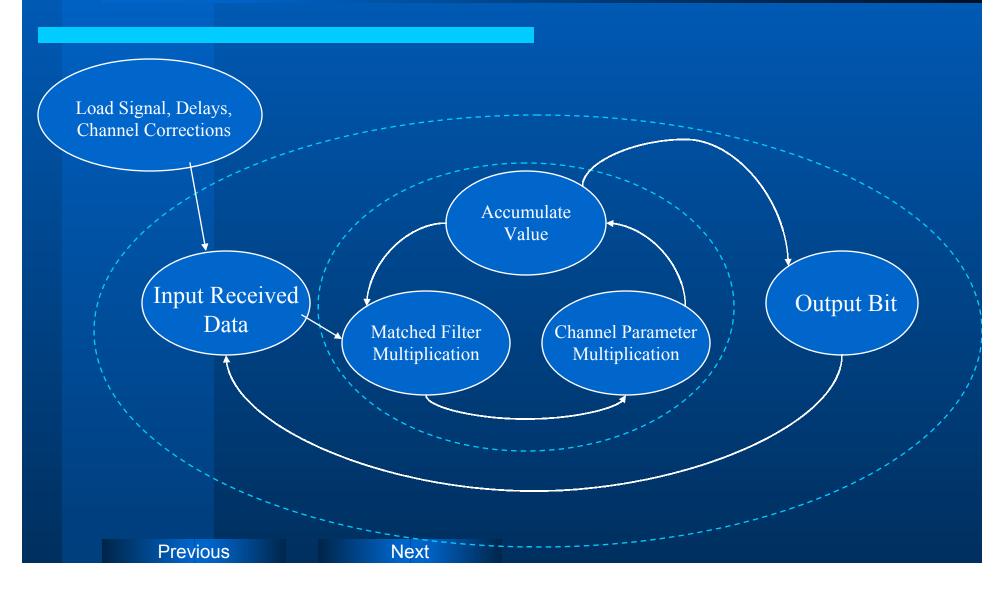

## What is it? How does it work?

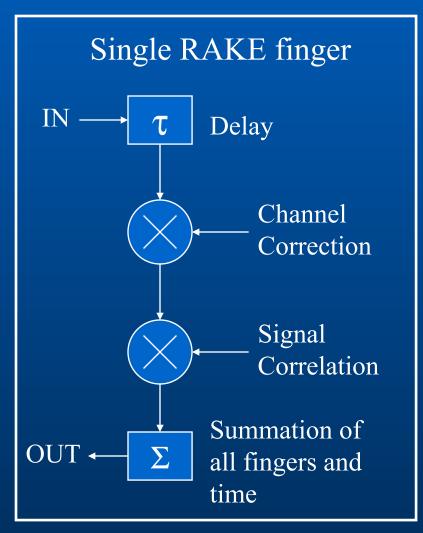

### **RAKE = Matched Filter for Channel Model**

### • RAKE Correlator

- Multiple paths increase performance

- Acts like a set of mini-correlators, called RAKE fingers

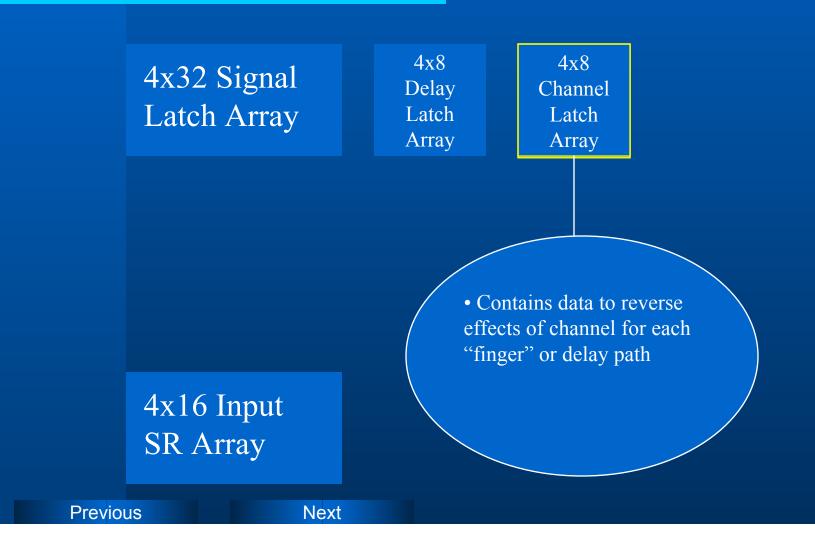

- Each finger is delayed and scaled for a given path (ie. A reflection from a building)

## Our specs

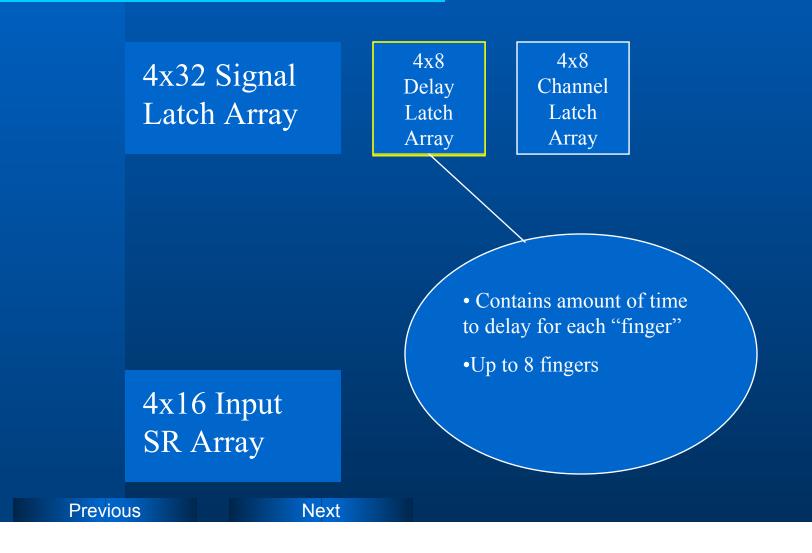

- Up to 8 RAKE fingers, Max delay of 16 chips

- 4 bit, 2's complement

- 32 chips/symbol, 1 bit/symbol

- Assume no inter-signal interference

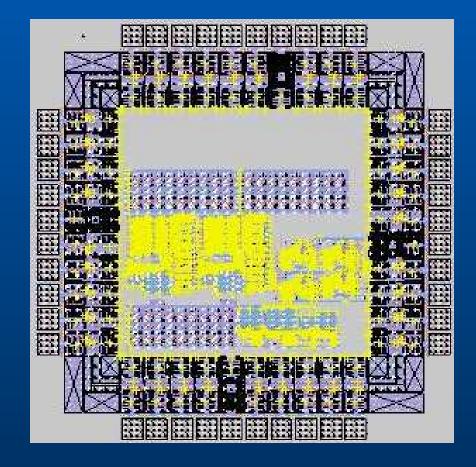

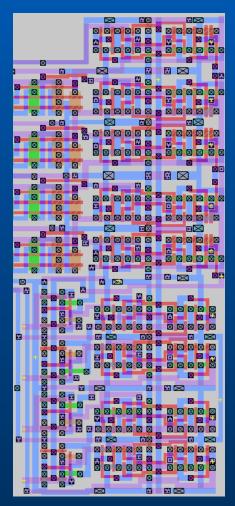

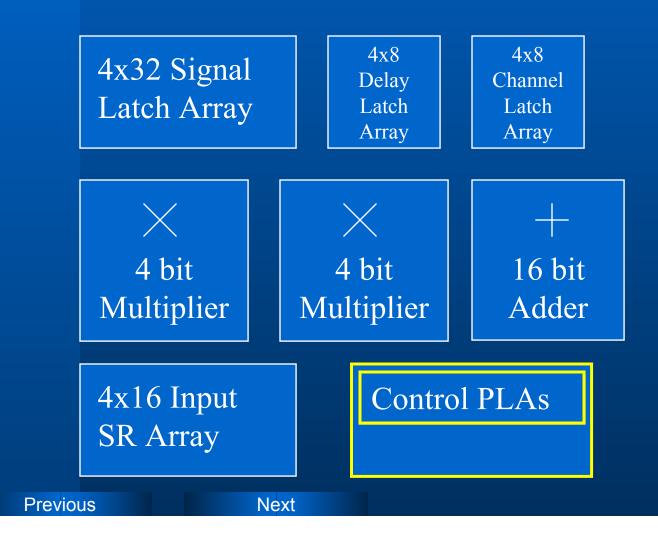

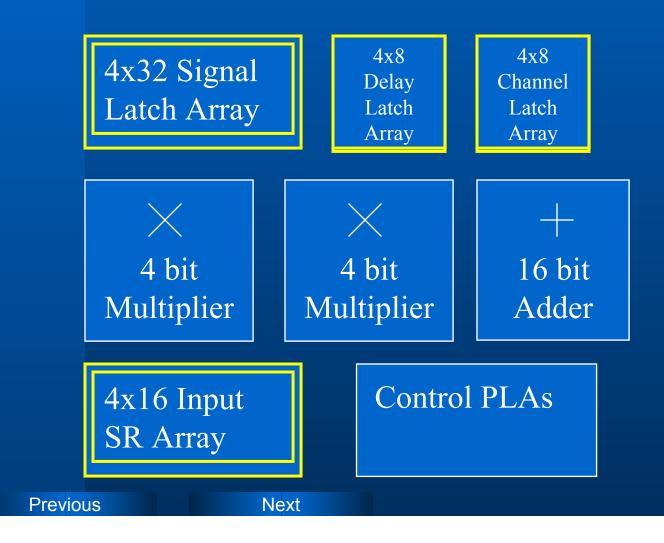

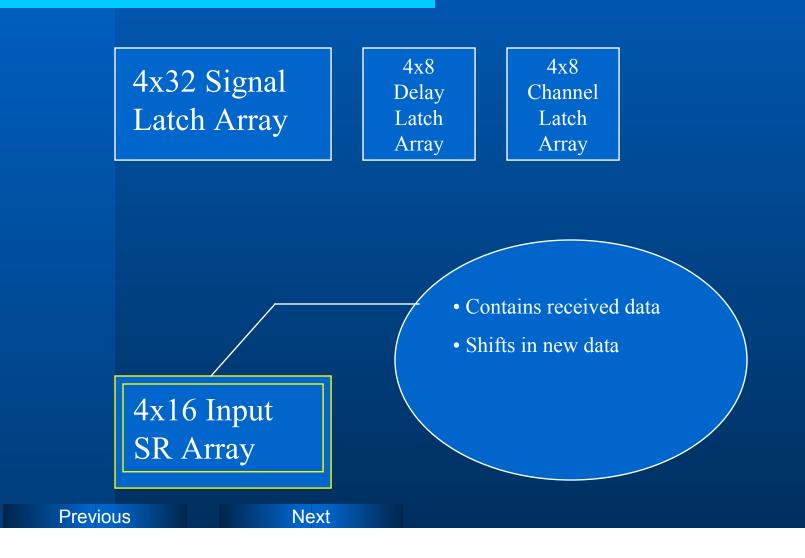

## Full Chip

Previous

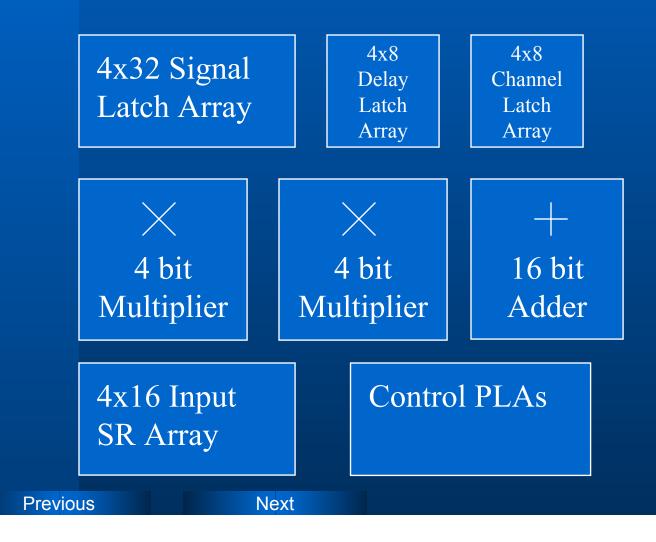

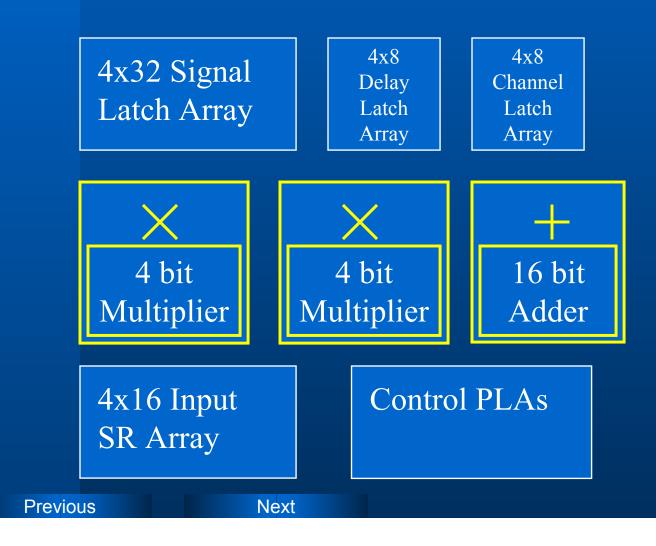

### **Basic** Floorplan

### Arithmetic

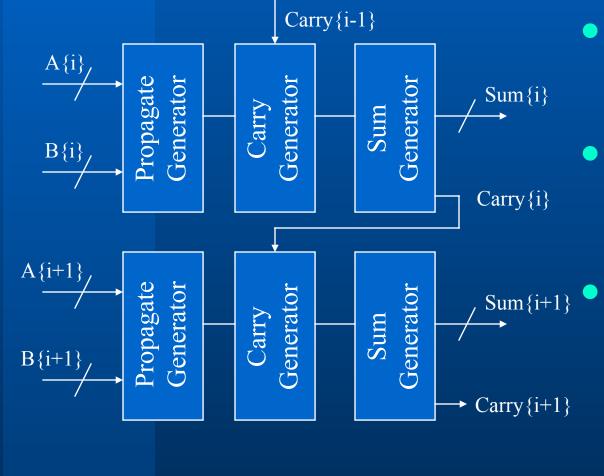

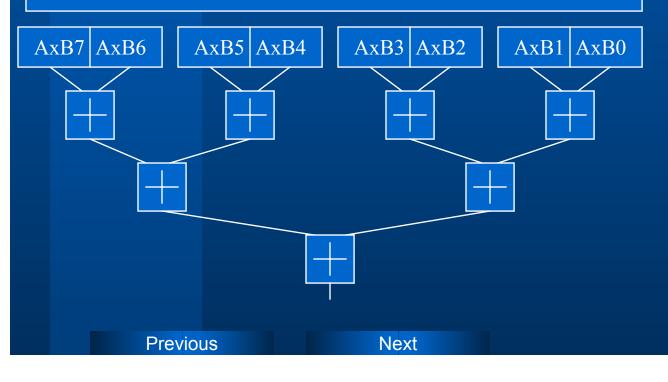

## Carry Look-ahead Adder

- Carry Look-Ahead is

3x faster than ripple

carry

- Carry Eqns

- Carry{i} = G{i}+P{i} C{i-1}

- $G{i} = A{i} \cdot B{i}$

- $P{i} = A{i}+B{i}$

- Used in Multiplier and Summation blocks

# Multiplier

- 1st Multiplier with a Manchester Adder and rounding of bits

- 2nd Multiplier with a CLA

### Control

### Control

### **Timing** Control

### **Major Points**

- Followed 2-phase clocking discipline

- Internal outputs all latched to clock B

- Internal Inputs all latched to clock A

### **Speed Optimizations**

- Split up main PLA into 4 sub PLAs

- Always full pipeline

- .5 μM process

- Carry Lookahead Adders

- Fast Tree Multipliers

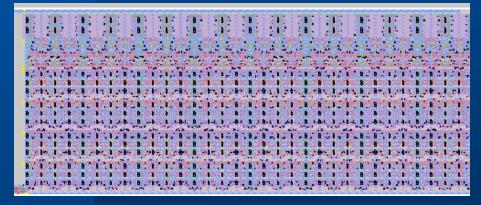

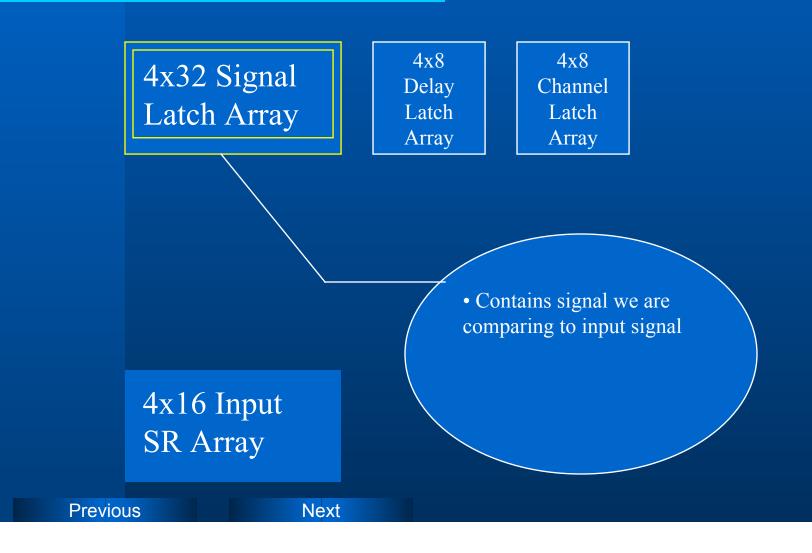

## Memory

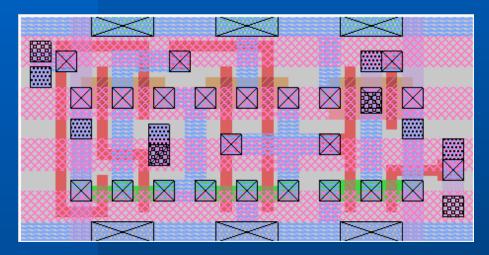

## Memory Layout

### Basic Latch Cell

#### Latch Array

Previous

## Testability

- "Test Control" chooses what appears on "Test Out"

- Final output is a 0 or 1, on "Output" pin

- Main PLA state bits are outputs

Reset Begin CLKA CLKB Input 0 Input 1 Input 2 Input 3 Signal in 0 Signal in 1 Signal in 2 Signal in 3 Delay in 0 Delay in 1 Delay in 2 Delav in 3 Channel in 0 Channel in 1 Channel in 2 Channel in 3

Data Ready Output Main PLA StBit0 Main PLA StBit1 Main PLA StBit2 Main PLA StBit3 Test Control 0 Test Control 1 Test Control 2 Test Control 3 Test Out 0 Test Out 1 Test Out 2 Test Out 3 GND GND GND Vdd Vdd Vdd

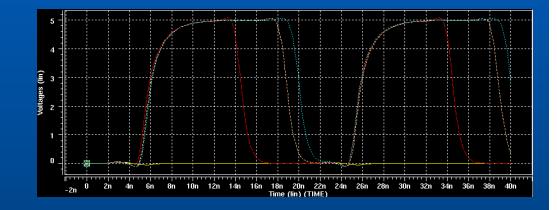

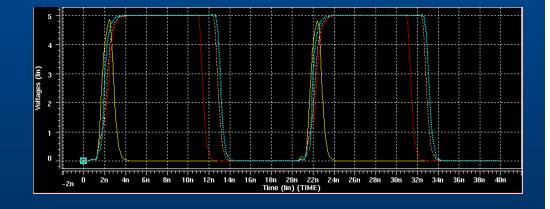

# Spice Analysis

### Multiplier plots ~8 ns

### 4 bit adder plots ~2.2 ns

Previous

### **Performance** Summary

**Max Delay Paths**

**Theoretical Maxima**

- 15.5 ns longest path in PLA

- 8 ns multiplier

- 2.2 ns four bit CLA (8 ns 16 bit adder)

Clock ~ 50 MHz

- Input ~ 6.4 Mchips/sec

- Output ~ 200 kbits/sec

### **Current Status**

Integrating and fitting components into pad frame

High level Integration testing

Developing test strategies

## Future...

Previous